#AMD ZEN 3 SERIES#

AMD Radeon RX 6000 Series : What You Need To Know!.RX 6900 XT, RX 6800 XT, RX 6800 : Features + Specifications!.Radeon RX 6000 vs GeForce RTX 30 : Faster + Cheaper!.AMD Infinity Cache Explained : 元 Cache Comes To The GPU!.

#AMD ZEN 3 FREE#

AMD Ryzen 5000 CPUs : Malaysia Price List + FREE Game!.AMD Ryzen 5 5600X In-Depth Review : A Leap Forward!.AMD Ryzen 7 5800X In-Depth Review : 8-Core Powerhouse!.AMD Ryzen 9 5950X In-Depth Review : 16-Core Behemoth!.But users can choose a 1:1:2 ratio if they have trouble overclocking memory. Therefore, the relationship between Infinity Fabric Clock ( fclk), Memory Controller Clock ( uclk) and Memory Clock ( mclk) remains the same.įor optimal performance, they are synchronous – in a 1:1:1 ratio. They continue to use the same IO die (IOD) as the 3rd Gen Ryzen processors. Only the Zen 3 core chiplet die (CCD) is new in the Ryzen 5000 series processors. Note : The temperature range below assumes an enclosed chassis, and an air-conditioned room.ĪMD Zen 3 Memory Overclocking : No Change The typical voltage range will vary according to usage, but basically, Zen 3 processors, like the Ryzen 5000 series, will support 0.2 V to 1.5 V.ĪMD Zen 3-based processors will also have the same temperature ranges as Zen- and Zen 2-based processors. In this example of the new Ryzen 9 5900X with a base clock of 3.7 GHz and a boost clock of 4.8 GHz, Precision Boost 2 will typically result in frequencies of 4.4 GHz to 4.6 GHz, even with 24 threads running at the same time.ĭespite the changes in the microarchitecture and SoC design, Zen 3 processors will continue to be engineered with the same voltage range as Zen- and Zen 2-based processors.

Precision Boost 2 will dynamically analyse and boost or dither the core clock speeds every 1 ms using the Infinity Fabric command and control functions. It is an opportunistic boost algorithm that drives the loaded cores to the highest possible frequency, until it hits any one of these limits :

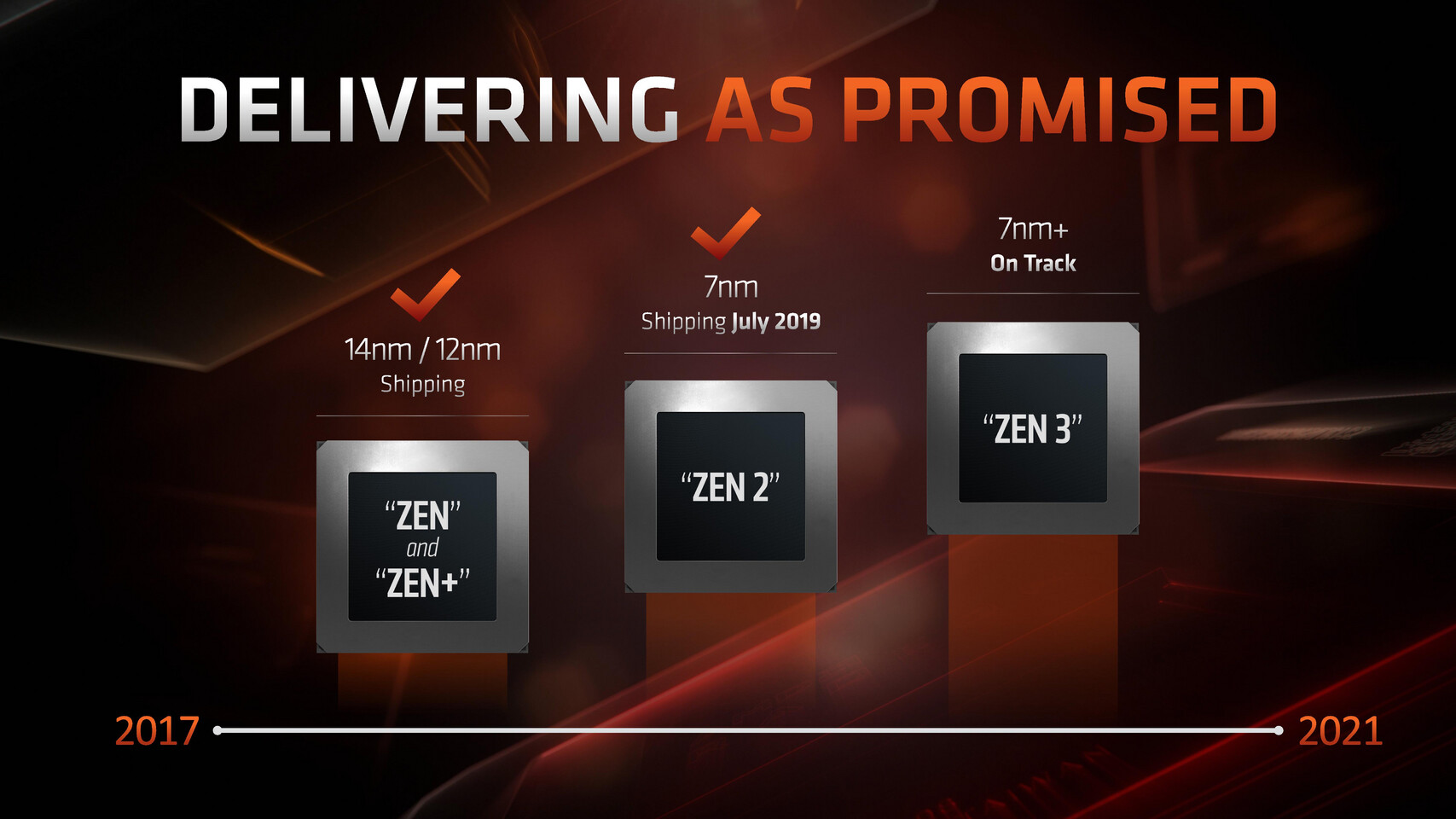

Precision Boost 2 in Zen 3 remains the same as that of Zen 2, just with higher frequencies to “play with”. They will both be manufactured using the same 7 nm TSMC process for CCD, and 12 nm Global Foundries process for IOD. The Matisse-era IOD remains the same – 2.09 billion transistors, with a die size of 125 mm².

That’s up from the 3.8 billion transistors and a die size of 74 mm² for the Zen 2 CCD. The new Zen 3 CCD has 4.15 billion transistors, with a die size of 80.7 mm². And it uses the same IOD from Matisse (Zen 2). Reads from CCD to IO are still 2X write, to conserve die area and transistor budget. On the other hand, AMD reused the chiplet design, with one or two CCDs (fabricated on 7 nm) paired with a 12 nm IOD (I/O Die). This unified CCD design completely eliminates CCX-to-CCX communication, greatly improving core-to-core latency. Zen 3 uses a unified complex, in which each CCD now contains a single CCX with a unified 32 MB 元 cache. In Zen 2, each CCD (Compute Die) is made up of two CCX (core complexes), each with a 16 MB 元 cache. In addition to micro architectural improvements, Zen 3 (Vermeer) also features SoC design changes. Rearchitect core/cache communication into a ring system.Unify all 元 cache in a CCD into a single contiguous element of up to 32 MB.Unify all cores in a CCD into a single unified complex consisting of 4, 6, or 8 contiguous cores.Reduce dependency on main memory accesses, reduce core-to-core latency, reduce core-to-cache latency.More flexibility in load/store operations.Overall higher bandwidth to feed the appetite of the larger/faster execution resources.Larger structures and better prefetching to support the enhanced execution engine bandwidth.Floating point FMAC is now 1 cycle faster.Floating point has increased bandwidth by +2 for a total of 6-wide dispatch and issue.Reduced latency for select float and int operations.New dedicated branch and st-data pickers for integer, now at 10 issues per cycle (+3 vs.Reduce latency and enlarge structures to extract higher instruction-level parallelism (ILP).Finer granularity in switching of op-cache pipes.

#AMD ZEN 3 CODE#

0 kommentar(er)

0 kommentar(er)